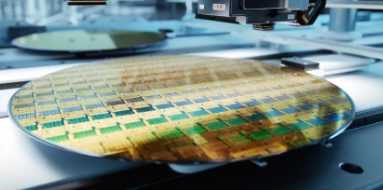

台积电周四在其位于南台湾科学园区(STSP)的Fab18举行了“量产和产能扩张仪式”。Fab18是使用其N3(3纳米级)工艺技术生产芯片的地方。该代工厂表示,其量产的3纳米芯片的良率很高,其N3技术系列将在未来许多年内为客户服务。

HVM中的N3

据报道,台积电于9月初在其N3制造工艺上启动了大批量制造(HVM)。目前第一批芯片已经生产和测试,所以正式宣布量产一般是为了表明晶圆代工厂的3nm级工艺适合量产,芯片良率“好”。对于台积电而言,N3是一个非常重要的工艺技术系列,因为它将是代工厂最后一个基于FinFET晶体管的通用节点,并且将为其客户提供至少10年的服务。事实上,台积电表示,N3及其后续产品将用于构建HVM的“五年内市值达1.5万亿美元的产品”。

与台积电的N5制造技术相比,该公司的N3生产节点有望提供10%至15%的性能提升(在相同的功率和晶体管数量下),降低25%至30%的功耗(在相同的频率和复杂性下),并将逻辑密度提高约1.6倍。N3几乎不提供任何SRAM缩放,因为它具有0.0199µm^²的SRAM位单元尺寸,与N5的0.021µm^²SRAM位单元相比仅小约5%。

标题单元格-第0列 N3E与N5 N3与N5

相同功率下的速度提升 +18% +10%~15%

功率降低@相同速度 -34% -25%~-30%

逻辑密度 1.7倍 1.6倍

虚拟机启动 2023年第二季度/第三季度 2022下半年

台积电3纳米级制造工艺的第一次迭代——N3也称为N3B——预计将被早期采用者仅用于特定应用,因为据报道它的工艺窗口相当窄。这可能会导致某些设计的良率降低。事实上,媒体报道称,台积电的大多数客户现在都在排队使用N3E制造技术,以SRAM微缩(即降低晶体管密度)为代价,改进工艺窗口、提高性能并进一步降低功耗。显然,N3E具有0.021µm^²SRAM位单元,与N5相比变化很小或没有变化。这将意味着SRAM密集型设计(绝大多数CPU、GPU和SoC)的裸片尺寸更大。

N3为芯片设计人员FinFlex提供了一种优化芯片尺寸和性能/功耗的强大方法。FinFlex让开发人员能够在一个模块内混合和匹配不同类型的标准单元,以准确优化性能、功耗和面积,这将特别受到倾向于利用晶体管性能和晶体管密度。